Description:

Learn to design an FPGA FIR filter using Xilinx Vivado High Level Synthesis in this 26-minute tutorial. Explore the process of creating a complete FIR filter in C, from setting up a basic ISE project to reprogramming the FPGA. Discover how to start an HLS project, implement the filter design, and work with filter coefficients. Follow along as the instructor demonstrates how to achieve a functional FIR filter in just 30 minutes of work. For those interested in C++ implementation, an updated version is available in a separate video link provided.

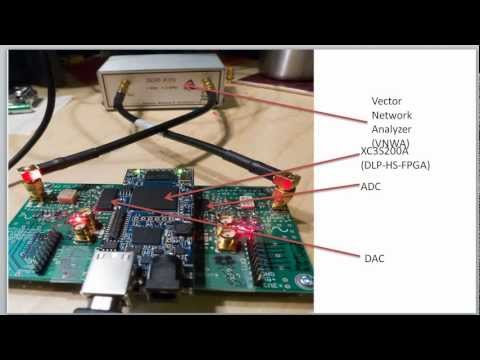

Xilinx HLS- FPGA FIR Filter Design in C in 30 Minutes

Add to list

#Engineering

#Electrical Engineering

#Circuits

#FPGA

#Vivado

#Programming

#Programming Languages

#C Programming

#Digital Signal Processing