Description:

Save Big on Coursera Plus. 7,000+ courses at $160 off. Limited Time Only!

Grab it

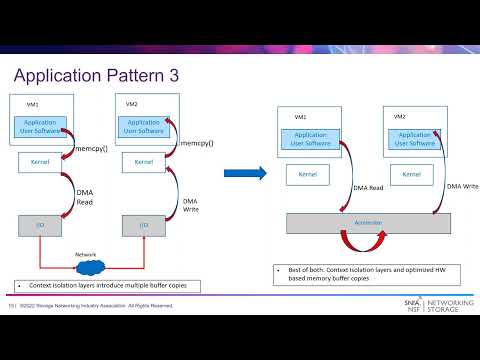

Learn about standardizing accelerator-assisted memory data movement and transformation in this technical webinar that explores the Smart Data Accelerator Interface (SDXI) and Compute Express Link (CXL) technologies. Dive into how SDXI Technical Work Group is developing an industry-open standard for memory-to-memory data movement and acceleration interface that emphasizes extensibility, forward compatibility, and I/O interconnect technology independence. Explore CXL's role as a Cache-Coherent Interconnect for Processors, Memory Expansion, and Accelerators, designed to support emerging applications like AI and Machine Learning. Understand legacy compute systems, current data movement standards, application patterns for buffer copies, memory expansion, and the integration of SDXI with CXL architecture. Industry experts from Dell Technologies, AMD, and Samsung discuss the technical specifications, use cases, and future roadmap of these complementary technologies that are reshaping high-speed communications and data movement in modern computing systems.

Read more

Memory Semantics and Data Movement with CXL and SDXI - Standards and Applications

Add to list

#Business

#Marketing

#Digital Marketing

#Conversion Rate Optimization

#CXL

#Computer Science

#Computer Architecture

#High Performance Computing

#Parallel Computing

#Heterogeneous Computing