Description:

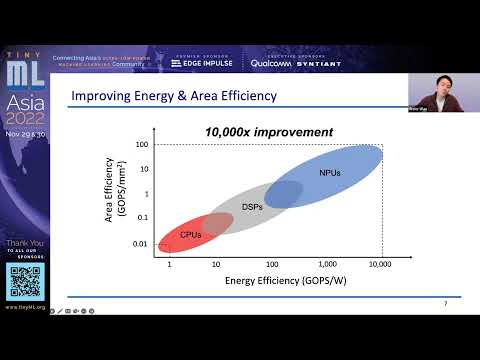

Explore software-driven TinyML hardware co-design in this insightful conference talk by Weier Wan, Head of Software-Hardware Co-design at Aizip. Delve into the importance of software-hardware co-optimization for achieving greater efficiency in TinyML systems. Learn about Aizip's approach to accelerator co-design services for IC companies, leveraging production-quality TinyML models across various applications. Discover the potential of processing-in-memory (PIM) AI accelerators and how they significantly reduce power consumption. Gain insights into Aizip's full-stack PIM co-design services, including silicon-verified PIM IPs, chip architecture design, PIM-optimized neural networks, and PIM-aware training frameworks. Understand how this comprehensive co-design approach ensures superior system-level energy efficiency without compromising accuracy or robustness compared to digital processors.

Software-Driven TinyML Hardware Co-Design for AI Power Smart Devices

Add to list

#Computer Science

#Machine Learning

#TinyML

#Artificial Intelligence

#Neural Networks

#Engineering

#Electrical Engineering

#Embedded Systems

#Social Sciences

#Sustainability

#Energy Efficiency