Description:

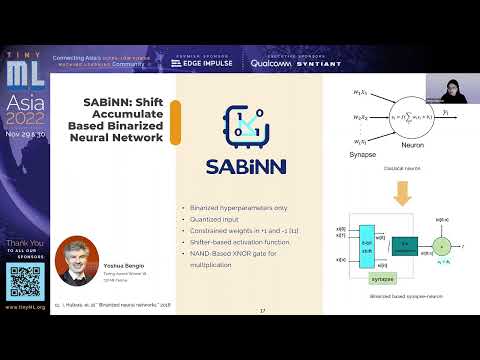

Explore power-efficient neural network-based hardware architecture for biomedical applications in this conference talk from tinyML Asia 2022. Delve into the SABiNN (Shift-Accumulate Based binarized Neural Network) approach, a 2's complement-based binarized digital hardware technique designed to address the challenges of deploying intelligent systems on edge devices with limited resources. Learn about deep compression learning techniques, including n-bit integer quantization and deterministic binarization, and how they contribute to reducing power consumption and model size. Discover the application of this method in a sleep apnea detection device, utilizing ECG and SpO2 data from real patient datasets. Examine the hardware implementation process, from FPGA validation to CMOS integration, and understand how the proposed model achieves medically acceptable accuracy while significantly reducing power consumption. Gain insights into the potential for developing fully integrated system-on-a-chip (SoC) biomedical systems for wearable applications.

Read more

Power Efficient Neural Network Based Hardware Architecture for Biomedical Applications

Add to list

#Computer Science

#Artificial Intelligence

#Neural Networks

#Engineering

#Electrical Engineering

#Circuits

#FPGA

#Machine Learning

#Quantization

#Programming

#Cloud Computing

#Edge Computing