Description:

Save Big on Coursera Plus. 7,000+ courses at $160 off. Limited Time Only!

Grab it

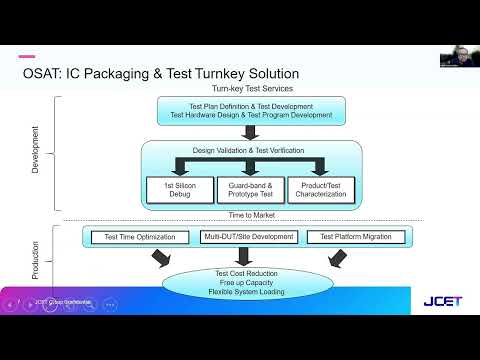

Learn about testing strategies for 3D integrated circuits in this technical presentation that explores the evolution beyond traditional chip testing. Delve into the complexities of testing methodologies for 3D IC development, including monolithic integration and advanced packaging technologies like 3D WLP, 2.5X/3D interposer/substrate integration, heterogeneous integration, and Chiplet solutions. Explore how OSATs and Foundries are leading turnkey testing solutions while examining the challenges in test methodologies and Design for Test (DFT) solutions. Master specific aspects of testing including function testability, defect debugging, test coverage, and economics. Gain insights into DFT methodology selection, Boundary Scan Description Language (BSDL) implementation, and IJTAG's role in comprehensive 3D IC testing strategies. Cover essential topics including semiconductor ecosystem mapping, test development, IC test fundamentals, scan testing, DFT standards, IEEE 1838 for 3D IC Stack, automatic test pattern generation, and equipment selection for testing platforms.

Read more

3D IC Test Strategy and DFT Methodologies for Advanced Packaging Technologies

Add to list