Description:

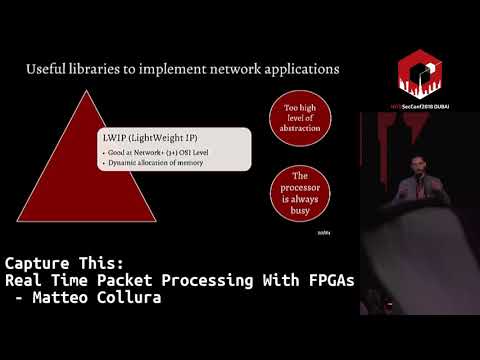

Explore real-time packet processing using FPGAs in this comprehensive conference talk from the Hack In The Box Security Conference. Dive into the limitations of Von Neumann architecture and discover how FPGAs offer a non-Von Neumann approach to overcome bottlenecks. Learn about FPGA internals, Xilinx fabric families, and the ZYNQ architecture. Examine useful libraries for implementing network applications and understand routing network connections. Delve into Gigabit Ethernet MAC and timing constraints as you work towards a fully hardware implementation. Investigate Ethernet at the ground level using conveyor belt and assembly chain models. Analyze Ethernet frame structure, preamble detection, and MAC and EtherType filters. Explore search algorithms, encryption environments, and witness demonstrations of MAC filtering, encryption, and decryption. Gain insights into achievements and future upgrades in FPGA-based packet processing.

Capture This - Real Time Packet Processing With FPGAs

Add to list

#Conference Talks

#Hack In The Box Security Conference

#Engineering

#Electrical Engineering

#Circuits

#FPGA

#Computer Science

#Cryptography

#Encryption

#Computer Architecture

#Von Neumann Architecture

#Computer Networking

#Network Engineering