Description:

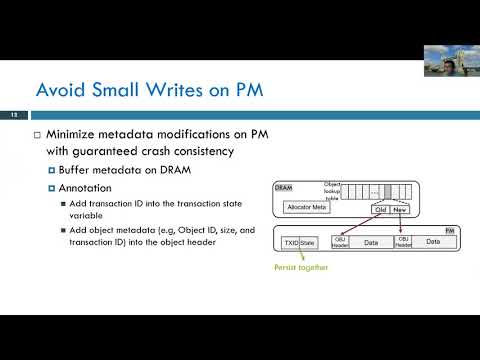

Explore a conference talk on ArchTM, an architecture-aware, high-performance transaction system for persistent memory. Delve into the innovative design principles aimed at avoiding small writes and encouraging sequential writes to optimize performance on persistent memory devices. Learn about ArchTM's variant of copy-on-write system, its scalable lookup table on DRAM, and the annotation mechanism for ensuring crash consistency. Discover how ArchTM's locality-aware data path in memory allocation increases coalescing writes inside PM devices. Examine the performance comparison between ArchTM and four state-of-the-art transaction systems, showcasing significant improvements in micro-benchmarks and real-world workloads on real persistent memory.

ArchTM - Architecture-Aware, High Performance Transaction for Persistent Memory

Add to list

#Conference Talks

#FAST (File and Storage Technologies)

#Business

#Performance Evaluation

#Computer Science

#Computer Architecture

#Persistent Memory