Description:

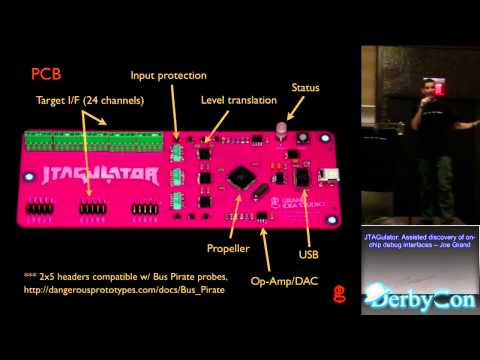

Explore on-chip debug interfaces and hardware hacking techniques in this DerbyCon 3.0 conference talk. Delve into the world of JTAG architecture, TAP controllers, and UART protocols as Joe Grand presents the JTAGulator, a tool for assisted discovery of debug interfaces. Learn about hardware design requirements, PCB layouts, and component selection for building such devices. Witness demonstrations of IDCODE scans, BYPASS scans, and UART scans, while understanding potential limitations. Gain insights into manually determining pin functions and identifying external interfaces, all essential skills for hardware security professionals and enthusiasts.

Jtagulator - Assisted Discovery of On-Chip Debug Interfaces

Add to list

#Conference Talks

#DerbyCon

#Engineering

#Electrical Engineering

#Embedded Systems

#Circuits

#PCB Design

#Information Security (InfoSec)

#Cybersecurity

#Computer Security

#Hardware Security

#UART